The *spider-web* array–a sparse spin qubit array **A** ASML UNSW Jelmer M. Boter,<sup>1,2</sup> Juan P. Dehollain,<sup>1,2,3</sup> Jeroen P. G. van Dijk,<sup>1,2,4</sup> Yuanxing Xu,<sup>1,2</sup> Toivo Hensgens,<sup>1,2</sup> Richard Versluis,<sup>1,5</sup> Henricus W. L. Naus,<sup>1,5</sup> James S. INTEL Clarke,<sup>6</sup> Menno Veldhorst,<sup>1,2</sup> Fabio Sebastiano,<sup>1,4</sup> and Lieven M. K. Vandersypen<sup>1,2,6,\*</sup> <sup>1</sup>QuTech, Delft University of Technology, Lorentzweg 1, 2628 CJ Delft, The Netherlands <sup>2</sup>Kavli Institute of Nanoscience, Delft University of Technology, Lorentzweg 1, 2628 CJ Delft, The Netherlands <sup>3</sup>School of Mathematical and Physical Sciences, University of Technology Sydney, Ultimo NSW 2007, Australia <sup>4</sup>Department of Quantum and Computer Engineering, Delft University of Technology, 2628 CJ Delft, The Netherlands <sup>5</sup>Netherlands Organization for Applied Scientific Research (TNO), P.O. Box 155, 2600 AD Delft, The Netherlands <sup>6</sup>Components Research, Intel Corporation, 2501 NE Century Blvd, Hillsboro, OR 97124, USA (Dated: October 4, 2021)

### Contents

- Elements of the Sparse Array achitecture

- Operation principle and surface code implementation

- Integration of classical control electronics

- Footprint , line scaling & heat discipation (1Million Qbits example)

### Array Design and Operation

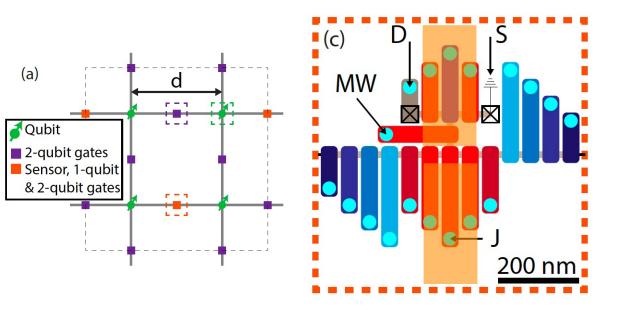

Sparse Array Architecture:

- Allows integration of control electronics (DC bias)

- Robust against inhomogeneities in the substrate

- Reduces crosstalk

- Requires coherent spin shuttling along um distances

Components:

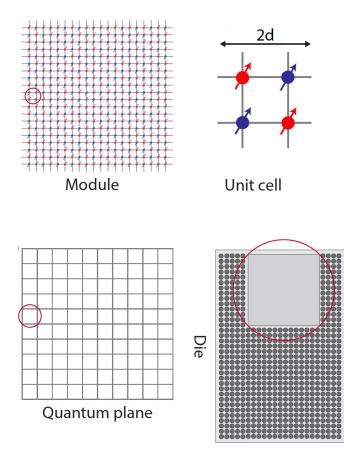

- Unit cell  $\rightarrow$  4 (2 Data+2 Ancilla ) Qubits  $\rightarrow$  d=10um

- Module → common DC bias & Readout

- Space in final die for extra electronics

### Unit Cell Operation

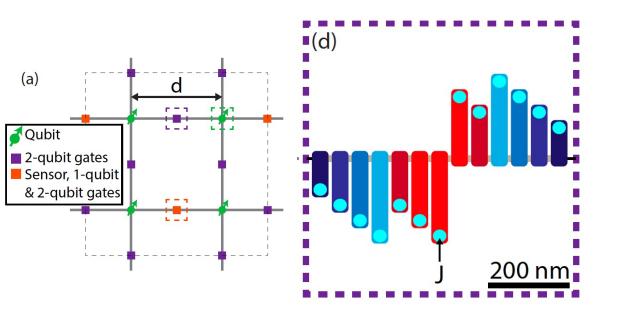

### 2 Qubit Gate Area

- 6 per unit cell

- 2 vertice gates (red) act both for confinment & tunneling to shuttling channel (C)

- 4 phase shifted signals at groups of 4 gates(blue) create travelling potential wave for shuttling (P)

- 2 plungers (for the spins) amd 1 exchange barrier gate J for 2 Qubit operations (fine)

| Region         | Regions in | Fine          | Coarse  | Pulsed |

|----------------|------------|---------------|---------|--------|

|                | unit cell  | $(1 \ \mu V)$ | (1  mV) | gates  |

| Two-qubit only | 6          | 3             | 2       | 5      |

### Unit Cell Operation

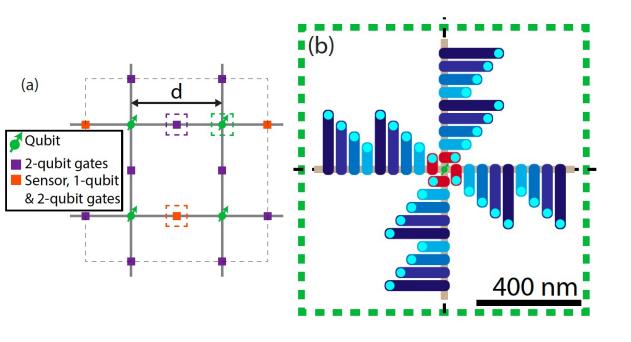

### **Idling Qubit Area**

- 4 per unit cell

- 4 barrier gates (red) act both for confinment & tunneling to shuttling channel (C)

- 4 phase shifted signals at groups of 4 gates (blue) create travelling potential wave for shuttling (P)

- Shuttling gate do not require DC bias by using large potential amplitude to eliminate inhomogeneities

| Region       | Regions in | Fine          | Coarse  | Pulsed |

|--------------|------------|---------------|---------|--------|

|              | unit cell  | $(1 \ \mu V)$ | (1  mV) | gates  |

| Qubit idling | 4          | -             | 4       | 4      |

### Unit Cell Operation

### Readout, 1 & 2 Qubit Gates

- 2 per unit cell

- 2 barrier gates (red) control tunneling to shuttling channel (C)

- 4 phase shifted signals at groups of 4 gates (blue) create travelling potential wave for shuttling (P)

- SET = 2 barriers (c)+ 1 plunger (C) + 2 Ohmics

- 1 Microwave line for driving single qubit gates

- 2 plungers (for the spins) amd 1 exchange barrier gate J for 2 Qubit operations (fine)

| Region          | Regions in<br>unit cell | Fine $(1 \ \mu V)$ | $\begin{array}{c} \text{Coarse} \\ (1 \text{ mV}) \end{array}$ |   |

|-----------------|-------------------------|--------------------|----------------------------------------------------------------|---|

| Qubit operation | 2                       | 7                  | 2                                                              | 6 |

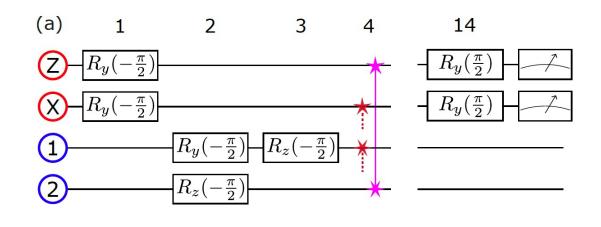

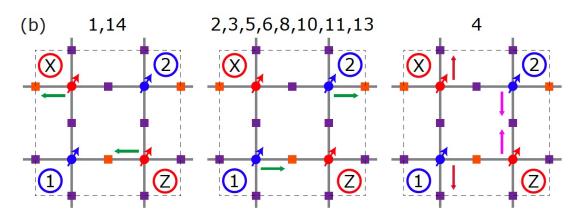

## Example: Surface code cycle

- Single Qubit rotations achieved by tuning EDSR microwave pulse

- Two Qubit gates achieved by the pulse applied to the J gate (SWAP based 3 step gate), (red purple stars)

- Readout only at the SC-ancilla qubits at the dedicated points

- Shuttling gate not require DC bias by using large

V amplitude to eliminate inhomogeneities

- Time of cycle:

$$t_{sc} = 22 t_{sh} + 14 t_{1q} + 8 t_{sw} + t_r$$

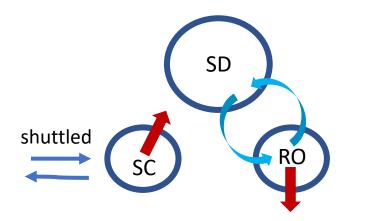

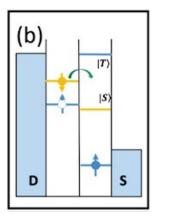

### Readout

#### Protocol

- PSB readout technique for higher T operation

- Readout Ancilla (RO) used to distinguise S-T transistion

- Transition detected by SET

- RO intialized and stored from and to the SET

#### Wiring

- i) Sequential readout in a module

- All drains connected to a single line

- Plungers controled by global demux outside

#### ii) Simultaneous readout

- Amplitute modulation: Different bias Vp for each SET plunger

- Frequency mod: RF readout of SET -> Local resonators -> large size

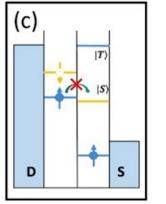

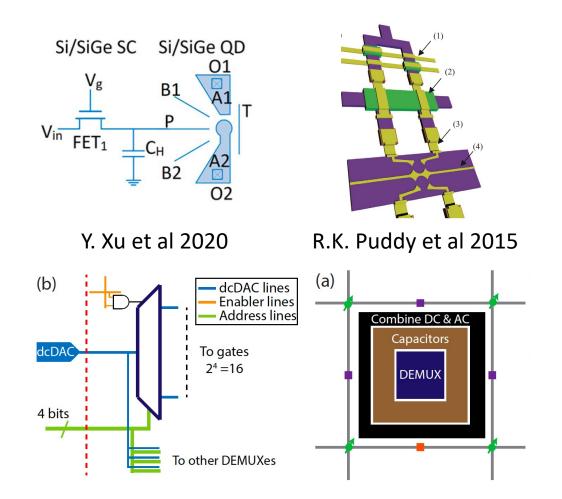

## Local Control Electronics

- Sample-and-hold scheme to apply a local DC bias to gates

- Two resolutions : Coarse (C) of ΔV=1uV (electron charge) & fine (F) ΔV=1mV (thermal noise)

- Two hold capacitors : $C_c = 0.16 \text{ fF } \& C_F = 0.16 \text{ fF}$

- Enabler line for each demux and dcDAC connection

- 64 DC bias gates per unit cell

- 1 to 16 demux (4 bits) in each open region

- 4 demuxes per unit cell

### Local Control Electronics

- Demux enabled by crossbar addressing in-module sequentialy all modules in parallel

- All array updated in a single module refresh cycle

| Gates                           | Routing                                                                                                                   |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Shuttling (blue)                | Source $\rightarrow$ gate                                                                                                 |

| Pulsed (red)                    | DC: source $\rightarrow$ local demux & S/H $\rightarrow$ gate AC: source $\rightarrow$ gate                               |

| Sensing dot<br>plunger (purple) | DC: source $\rightarrow$ local demux & S/H $\rightarrow$ gate<br>AC: source $\rightarrow$ global demux $\rightarrow$ gate |

| Drain contacts                  | Measurement device $\leftarrow$ Ohmic                                                                                     |

# Local Control Electronics

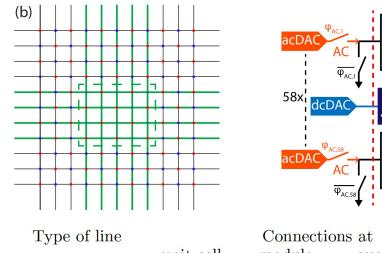

| acDAC<br>AC<br>$\overline{\phi_{Ac_1}}$<br>58x<br>dcDAC | To other<br>unit cells<br>To gate       |

|---------------------------------------------------------|-----------------------------------------|

| acDAC $AC$ $AC$ $\phi_{AC,S8}$                          | To other<br>unit cells<br>DC<br>To gate |

| Type of line           | Connections at |                                                   |                                                                                      |

|------------------------|----------------|---------------------------------------------------|--------------------------------------------------------------------------------------|

|                        | unit cell      | module                                            | quantum plane                                                                        |

| DC biasing             | 9              | $4N_b + 5$                                        | $M_b^2 + 4N_b + 4$                                                                   |

| Shuttling              | 4              | 4                                                 | 4                                                                                    |

| Pulsed signals<br>& MW | 58             | 58                                                | 58                                                                                   |

| Logical operations     | 4x             | $4N_bx$                                           | $4N_bM_bx$                                                                           |

| Readout                | 3              | $\frac{2\log_2 N_r - \log_2 r + 1}{\log_2 r + 1}$ | $\frac{M_r^2 + 2\log_2 N_r - \log_2 r}{\log_2 r}$                                    |

| Total                  | 74 + 4x        | $4N_b(1+x)+2\log_2 N_r-\log_2 r+68$               | $     M_b^2 + M_r^2 +      4N_b(1 + M_b x)      +2 \log_2 N_r -      \log_2 r + 66 $ |

- AC signals (MW and pulsed) generated remotely by acDAC before circuit that combines AC and DC

- Crossbar network design to control barrier gate to enable • surface codes.

- 4 enablers + 4 address 1 dcDAC= 9 lines for biasing p.u.c. •

- Only enabler scale with the # of u.c. as 4Nb per module ٠

- Address lines and dcDAC shared between all u.c. ٠

- Shuttling (4) and AC signals (58) are shared in the array ٠

- For crossbar depends on the encoding for logical qubits  $\chi$ ٠

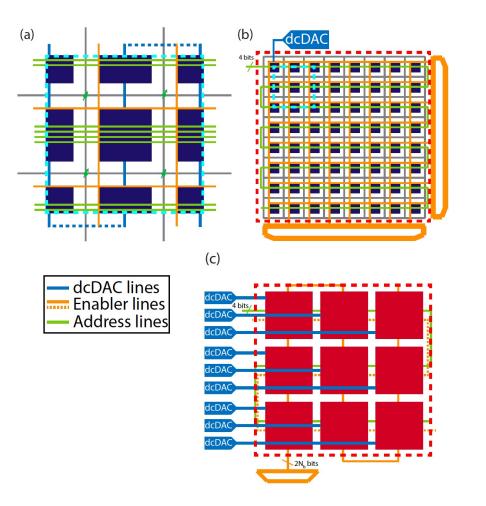

# Million Qubit Array example

#### Footprint

Capacitor  $A_c = 450 \text{ um}^2$ Demux (40 nm tech) = 180 um<sup>2</sup> Qubit pitch d = 12-14 um  $\rightarrow$  50nm QD pitch  $\rightarrow$  260 QD per lattice arm

#### **Heat Dissipation**

- Parasitic capacitances of the  $P_p = \frac{1}{2}C_p v_p^2 f_p$  routing lines

- Discipation for the sample-and-  $P_d < 140 \text{ nW}$  hold circuits for 4 Demux p.u.c.

- AC thin lines power discipation  $P_t = 1.1 \frac{\mathrm{nW \, ns^2}}{\mathrm{V^2}} \, \left( v_t f_t \right)^2$

Million Qubit Array:

- $2^{20}$  (  $10^{6}$ ) qubits, or U =  $2^{18}$  unit cells

- 256 modules maximum clock frequency of the demux biasing to f<sub>b</sub>=6 GHz

- Rent's exponent = 0.43 + crossbar = 0.5

Area covered by the quantum plane = 177 mm<sup>2</sup> Duration of a surface code cycle:

- Shuttling time t<sub>sh</sub> 50 ns [B. Buonacorsi et al.]

- Gate time  $t1_{q}$ ,  $t_{sw}$  =25 ns [R. C. C. Leon et al.]

- PSB Readout time  $t_r = 1 \mu s$  [E. J. Connors et al.] Total cycle time,  $t_{sc} = 6 \mu s < T_2^* = 20 \mu s$

Power discipation 100mW  $\rightarrow$  0.2 K self heating

# Thanks!!